- Témaindító

- #1

- Csatlakozás

- 2023.05.28.

- Üzenetek

- 23,225

- Reakció pontszám

- 528

- Díjak

- 6

- Kor

- 33

x64 | File size: 15.1 GB

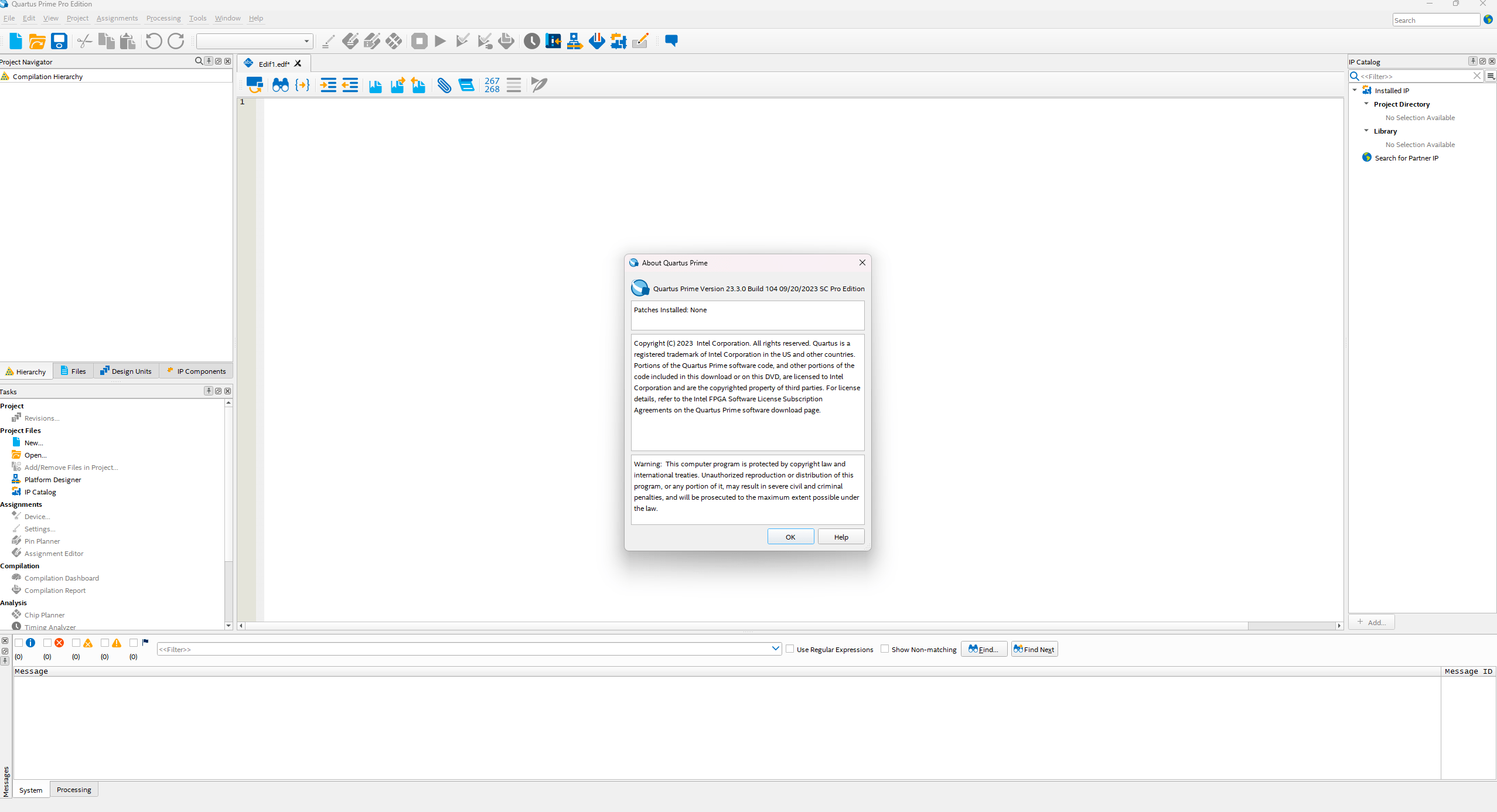

This user guide describes basic concepts and operation of the Intel® Quartus® Prime Pro Edition design software, including GUI and project structure basics, initial design planning, use of Intel FPGA IP, and migration to Intel® Quartus® Prime Pro Edition. This software provides a complete design environment for the most advanced Intel® Agilex™ , Intel® Stratix® 10, Intel® Arria® 10, and Intel® Cyclone® 10 GX FPGA and SoC designs.

The Intel® Quartus® Prime software GUI supports easy design entry, fast design processing, straightforward device programming, and integration with other industry-standard EDA tools. The user interface makes it easy for you to focus on your design-not on the design tool. The modular Compiler streamlines the FPGA development process, and ensures the highest performance for the least effort.

The Intel® Quartus® Prime Pro Edition software offers flexible design methodologies, advanced synthesis, and supports the latest Intel® FPGA architectures and hierarchical design flows. The Compiler provides powerful and customizable design processing to achieve the best possible design implementation in silicon. The following features are unique to the Intel® Quartus® Prime Pro Edition

-Hyper-Aware Design Flow-use Hyper-Retiming and Fast Forward compilation to reach the highest performance in Intel® Agilex™ and Intel® Stratix® 10 devices.

-Intel® Quartus® Prime Pro Edition synthesis-integrates new, stricter language parser supporting all major IEEE RTL languages, with enhanced algorithms, and parallel synthesis capabilities. Added support for SystemVerilog 2009.

-Hierarchical project structure-preserve individual post-synthesis, post-placement, and post-place and route results for each design instance. Allows optimization without impacting other partition placement or routing.

-Incremental Fitter Optimizations-run and optimize Fitter stages incrementally. Each Fitter stage generates detailed reports.

-Faster, more accurate I/O placement-plan interface I/O in Interface Planner.

-Platform Designer-builds on the system design and custom IP integration capabilities of Platform Designer. Platform Designer in Intel® Quartus® Prime Pro Edition introduces hierarchical isolation between system interconnect and IP components.

-Partial Reconfiguration-reconfigure a portion of the FPGA, while the remaining FPGA continues to function.

-Block-Based Design Flows-preserve and reuse design blocks at various stages of compilation.

System Requirements

OS:Windows* 10/Windows Server* 2012 Enterprise/Windows Server* 2016 Enterprise/Windows Server* 2019 Enterprise

Screen :

What's New

HOMEPAGE

Code:

⚠

A kód megtekintéséhez jelentkezz be.

Please log in to view the code.

Code:

⚠

A kód megtekintéséhez jelentkezz be.

Please log in to view the code.

Code:

⚠

A kód megtekintéséhez jelentkezz be.

Please log in to view the code.